历时一个月零一天,WindowsKernel的保护模式这块终于完结了!(撒花撒花)

非常感谢 lzyddf 师傅的博客,知识点罗列的非常清晰;非常感谢 Bayerischen 师傅对于一些难点的答疑解惑。保护模式的七篇博客仍会在接下来处于一个动态更新的状态,因为这块内容确实生涩,我还有诸多不理解之处,等在后续的学习中有了新的理解后会对博客再做修改。

0x01 控制寄存器

控制寄存器共有五个,分别是

Cr0 Cr1 Cr2 Cr3 Cr4

下面分别介绍

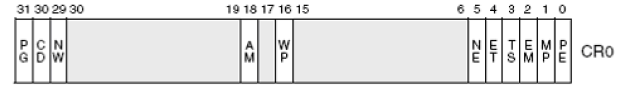

Cr0寄存器

CR0寄存器中含有控制处理器操作模式和状态的系统控制标志

PE位:启用保护(Protecction Enable)标志

PE=1:保护模式

PE=0:实地址模式

这个标志仅开启段级保护,不代表会启用分页机制

MP位:监控协处理位(Moniter coprocessor)

用于控制WAIT/FWAIT指令与TS标志的交互作用。

MP=1、TS=1:那么执行WAIT指令将产生一个设备不存在异常

MP=0:TS标志不会影响WAIT的执行。

EM位:模拟协处理器位(Emulate coprocessor)

EM=1:不能使用协处理器

EM=0:允许使用协处理器

PG位:分页机制允许(Paging Enable)标志

PG=1:开启了分页机制

PG=0:未开启分页机制

在开启这个标志位之前必须已经或者同时开启PE标志

PG=0且PE=0:处理器工作状态为实地址模式

PG=0且PE=1:处理器工作状态为没有开启分页机制的保护模式

PG=1且PE=0:不存在。在PE没有开启的情况下无法开启PG

PG=1且PE=1:处理器工作状态为开启了分页机制的保护模式

WP位:写保护(Write Proctect)标志(仅对内核模式有效)

对于Intel 80486或以上的CPU,CR0的16位是写保护标志

当设置该标志时,处理器会禁止超级用户程序(例如特权级0的程序)向用户级只读页面执行写操作

当某进程CPL<3的时候:

- 如果 WP=0 可以读写任意用户级物理页,只要线性地址有效(其通常用于使页的只读属性失效)

- 如果 WP=1 可以读取任意用户级物理页,但对于只读的物理页,则不能写

Cr1寄存器

被系统保留,暂不被使用

Cr2寄存器

Cr2寄存器用于出现页异常时报告出错信息。当CPU访问某个无效页面时,会产生缺页异常,此时,CPU会将引起异常的线性地址存放在CR2中。

例如,当CPU访问某个物理页,但PDE/PTE的P位为0时,会产生缺页异常。缺页异常一旦发生,CPU会将引起缺页异常的线性地址存储到Cr2中,此时,操作系统的处理程序开始对异常进行处理。若处理结束后,虽然PDE/PTE的P位为0,但实际上它被写进了页面,这时,处理程序会将数据从页面中读出,再挂上一个有效的物理页,让程序接着往下跑,程序往下跑时,操作系统必须要记录程序原先已经跑到了哪里,此时,Cr2便派上了用场,因为产生异常时的线性地址存在了Cr2中。但如果异常处理程序检测到用户访问的页面是一个未分配的页面。这时,操作系统会报告一个异常,告诉我们在哪里发生了错误。

通过上例,Cr2的作用就很明了了,若没有Cr2寄存器,当进入异常处理程序时,将找不到回去的线性地址。

Cr3寄存器

CR3含有存放页目录表页的物理地址,因此CR3也被称为PDBR(Page-Directory Base address Register,页目录基地址寄存器)。(前面连着好几章讲的内容都和Cr3有关,如果现在还不知道Cr3是干嘛的不用再看了눈_눈

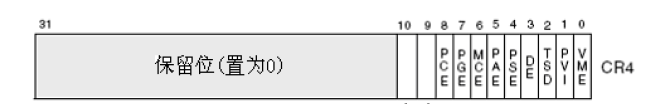

Cr4寄存器

Cr4寄存器在新式的CPU中才出现,这里只做简略介绍

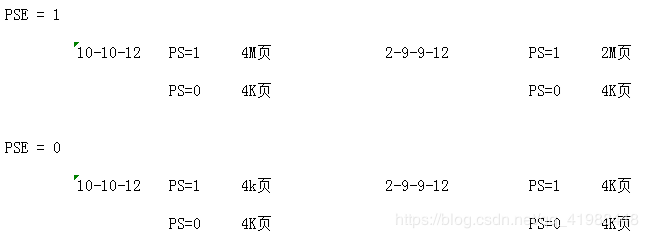

PAE:

PAE=1:2-9-9-12分页

PAE=0:10-10-12分页 \

PSE:

0x02 CPU缓存

CPU缓存是位于CPU与物理内存之间的临时存储器,它的容量比内存小的多,但是交换速度(读写速度)比内存要快得多。CPU缓存大小因CPU的不同而有很大的区别,有几K、几十K、几百K、甚至上M,这决定于CPU的版本。这里我们要将 CPU缓存 与 TLB(转译后备缓冲器) 做一个区分。CPU缓存存储的是物理地址与内容之间的对应关系,而TLB存储的则是线性地址与物理地址之间的对应关系。这二者是有区别的。

有了CPU缓存,当CPU再去查找/读取某一个线性地址对应的物理页时,所进行的是这样的操作:

- 先查TLB,找到线性地址对应的物理地址

- 再找CPU缓存,找到它的内容

CPU缓存的大小决定了CPU的执行速度(CPU缓存越大,速度越快,当然也会越贵)

之前将PDE/PTE时刻意跳过了两个属性位没有讲,这两个属性位与CPU缓存有关,这里补上。

PWT(Page Write Through)

PWT=1:写Cache的时候也要将数据写入内存中

PWT=0:写Cache的时候就只是写Cache,是否要映射到内存由CPU缓存控制器自己决定 \

PCD(Page Cache Disable)

PCD=1:禁止某个页写入缓存(直接写入内存)

比如:做页表用的页,已经存储在TLB中,可能就不需要再做缓存,所以它的PCD一定为1